¶ NTN AI-Acceleration

¶ NTN AI-Acceleration Overview

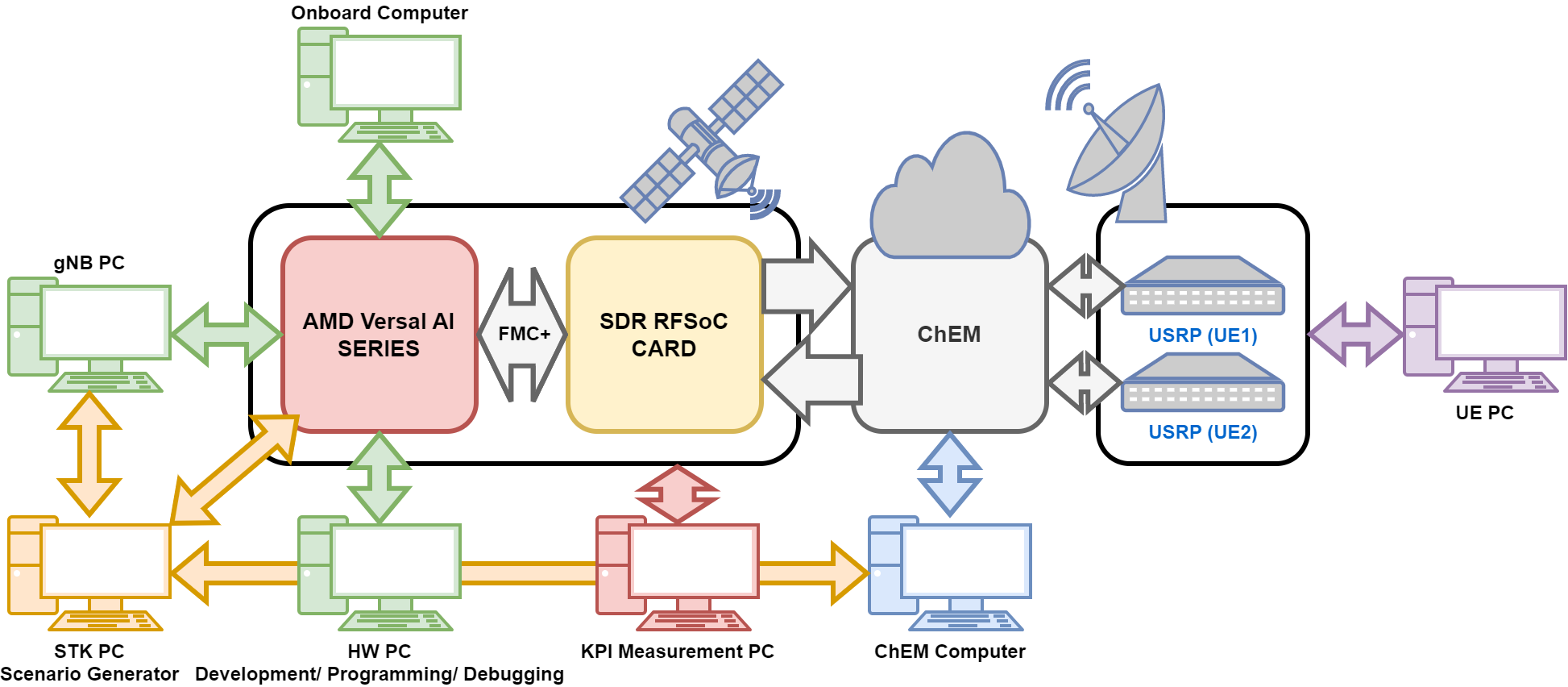

The project aims to enhance satellite communication through the use of AI-based signal processing techniques. It involves developing methods for signal identification, spectrum monitoring, sharing, and demodulation using an off-the-shelf AI chipset. The laboratory testbed validates these techniques in both on-ground and on-board scenarios. Success could lead to more efficient and reliable satellite communication, benefiting various industries. However, challenges include algorithm optimization and hardware constraints.

¶ Hardware and Software

The hardware implementation strategy for the project involves utilizing specific architectures and devices, including the Versal AI Core (VCK190) from AMD/Xilinx, the Versal AI Edge (VE2302 EVK) from iWave, and the Zynq UltraScale+ RFSoC (ZRF-FMC-4A4D) from HiTechGlobal. These platforms are chosen to harness their strengths in AI processing, edge computing, and RF capabilities.

The project aims to effectively integrate these components to develop and validate AI-based signal processing techniques for satellite communication. This approach aligns with the project's focus on practical implementation using off-the-shelf hardware. However, ensuring seamless coordination between AI and RF processing poses potential challenges.

¶ AI platform

The AI platform for the AISTT system is composed of two main components:

- iWave's Versal AI Edge SOM Development platform: This component is a critical part of the AI platform and is used for AI-based signal processing tasks. The Versal AI Edge SOM Development Platform, likely built on Xilinx's Versal architecture, provides the necessary computational power and AI capabilities for signal identification, spectrum monitoring, sharing, and demodulation.

- HiTech Global's Xilinx Zynq UltraScale+ RFSoC FMC+ (Vita57.4) Platform: This component, based on the Xilinx Zynq UltraScale+ RFSoC architecture, is specifically designed for RF signal processing. It's crucial for tasks such as signal reception, RF front-end processing, and interfacing with the satellite communication hardware.

The AI platform and the RF front-end are connected using the four gigabit transceivers (GTY) available on both platforms. These transceivers are accessible through the FMC+ HPC VITA 57.4 connector. Each GTY can support a full-duplex serial connection with a speed of up to 28Gbps. In total, the four transceivers provide a combined bandwidth of 112Gbps, facilitating high-speed data transfer between the AI platform and the RF front-end. By combining these two platforms, the AISTT system can leverage the AI processing capabilities of the Versal AI Edge SOM while utilizing the RF and high-speed data processing capabilities of the Zynq UltraScale+ RFSoC FPGA. This enables the system to perform advanced AI tasks and handle RF-related functions simultaneously.

In the setup testbed, various auxiliary devices are essential to ensure proper utilization and testing:

- Onboard Computer (OBC): The onboard computer is a critical component for satellite systems. It's responsible for managing and controlling various subsystems and processes on the satellite itself. In this context, it might be used to oversee signal processing, communication, and other functions.

- Scenario Generator PC: The scenario generator PC, runing Systems Tool Kit software (STK), creates and simulate different scenarios that the satellite system might encounter. These scenarios can include various signal conditions, interference patterns, and communication challenges. This PC helps in testing the system's performance under diverse conditions.

- Base Station PCs (gNodeB or gNB): The base station PCs are responsible for managing communication with the satellite. It likely simulates ground-based communication infrastructure and are used to establish communication links, exchange data, and assess the satellite's communication capabilities. These computers should be able to run the Open-Air Interface (OAI) stack including:

- Open source implementation of Radio Access Network(RAN) and Core Network(CN) for 4G and 5G

- Control plane and User plane separation

- Split of Centralized Unit(CU), Distributed Unit(DU) and Radio Unit(RU). Supports IF5 and IF4.5 functional split ( Option 8 and Option 7-1 in the 3GPP)

- OAI containers(Docker) for 4G/5G base-station and UE

- Hardware PC: This PC is a general-purpose computer used for managing hardware-related tasks. It is used for development the HW design, programing, debuging, configuring and managing the testbed's hardware components, such as data converters, transceivers, and ML processing hardware.

¶ Users terminals

The user terminal component of the design consists of the following key elements:

- USRPs (Universal Software Radio Peripherals): The selected hardware for the SDR is National Instruments USRP X310 These software-defined radio (SDR) devices used for transmitting and receiving radio signals. USRPs are flexible and can be programmed to work with various wireless communication standards. In this context, they likely serve as transceivers, allowing the user terminal to communicate with a satellite or ground station.

- UE PC (User Equipment PC): The User Equipment PC is a computer that serves as the user's interface and control center for the user terminal. It's responsible for running software applications and managing the communication process between the USRPs and the satellite or ground station. This PC might host communication protocol stacks, signal processing algorithms, and user interfaces for configuring and monitoring the terminal's operation. Like gNB PC's, this computer should be able to run the Open-Air Interface (OAI) stack including:

- Open source implementation of Radio Access Network(RAN) and Core Network(CN) for 4G and 5G

- Control plane and User plane separation

- Split of Centralized Unit(CU), Distributed Unit(DU) and Radio Unit(RU). Supports IF5 and IF4.5 functional split ( Option 8 and Option 7-1 in the 3GPP)

- OAI containers(Docker) for 4G/5G base-station and UE

¶ Channel modeling

The channel modeling system comprises several components:

- RFSoC ZCU111: This hardware component, based on the Xilinx Zynq UltraScale+ RFSoC architecture, is a versatile platform for RF signal processing. It's used for tasks such as signal reception, processing, and data conversion. The ZCU111 handles the RF-side functions, which are crucial for channel modeling.

- ChEM Computer: The ChEM computer serves as an intermediate component between the user and the RFSoC ZCU111. Its responsibilities include:

- User Interface: It runs a graphical user interface (GUI) that allows users to configure various parameters for channel modeling. Users can input settings and requirements through this interface.

- Configuration Management: The ChEM computer receives user configurations from the GUI and sends them to the RFSoC ZCU111. These configurations likely include parameters related to the channel model, signal characteristics, and simulation scenarios.

¶ Experiment

The AISTT design architecture serves as the backbone of KPI measurement system. This includes subsystems such as AI payload, data generator, operations hardware, auxiliaries, and payload firmware. The subsequent sections detail GUI functionalities and AI operation and optimization methods. Each section describes thoroughly the associated hardware, software and required connectivity procedures. The testbed incorporates a diverse set of software, firmware, and hardware components. These components interact seamlessly to facilitate accurate KPI measurements. MATLAB, STK, VIVADO, and Linux are used to deploy, control, and communicate with the components.

The testbed relies on a network of power and data lines to connect its various components. These lines are equipped with connectors tailored to each component's requirements, ensuring smooth data flow and power distribution. The power and data flow within the testbed is meticulously designed to optimize performance. Voltage and current sensors monitor power consumption, contributing to accurate measurements such as measuring the power consumed by the AI board during algorithm implementation.